The appetite for systems on chips

Heralded by many as the Holy Grail of system design, SoCs unite multiple subsystems, saving circuit board space and power and enhancing performance. In 1995, SoCs had hundreds of thousands of gates, a single programmable microprocessor core, and on-chip memory. Today, the digital, analog, and RF functions found on a single chip are far more diverse. A good instance is the super optical-disk controller for DVD systems developed by Matsushita, of Osaka, Japan. This SoC combines the contents of three chips in one, reducing the power and space requirements while more than doubling playback speed.

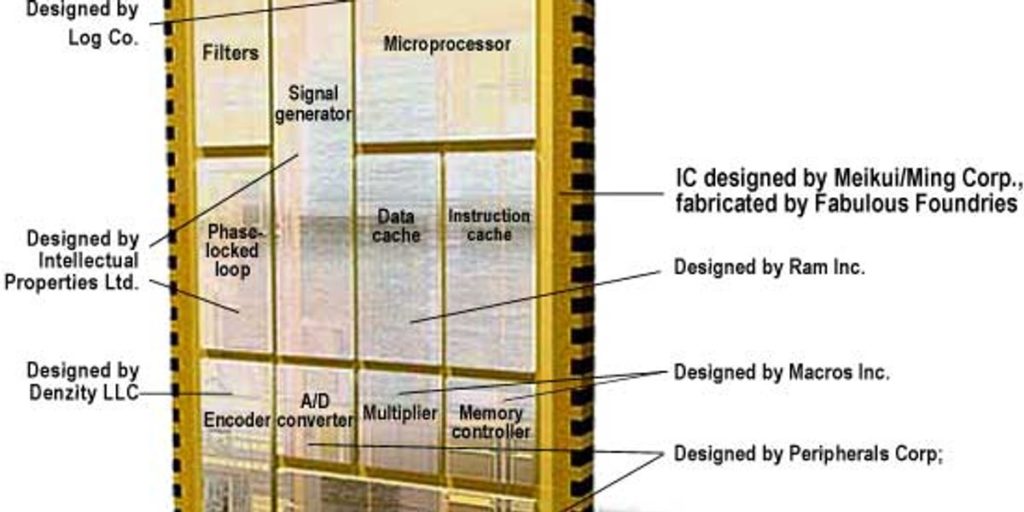

An SoC comprises cells and potentially reusable IP blocks that can be recycled from application to application. Examples include digital signal-processor cores like the TMS320C55x family from Texas Instruments and the ADSP-21535 from Analog Devices. Memory subsystems can also be purchased from third-party vendors as blocks for embedding into the SoC.

To facilitate IP portability, the SoC industry founded the Virtual Socket Interface Alliance (VSIA) in 1996. The alliance promotes the mix and match of IP from multiple sources, as well as simplifying the development of stimulus-response checks called test benches. Using the concept of virtual sockets, which define standard interfaces, pre-verified IP can, in principle, be assembled on both a functional and a physical level. In other words, the parts will both play together electronically as a system and fit together on a chip.

To ensure high reliability, VSIA recently formed a study group from representatives of seven organizations (ARM, Fujitsu, IC-Cad Solutions, Intel, the VSIA Japanese Special Interest Group [JSIG], Mentor Graphics, and Synopsys). Their goal is to formulate a comprehensive approach to measuring the factors that determine IP and SoC quality. The factors include design authoring (which defines and documents the arrangement and interaction of functional blocks), design verification, system-level validation, manufacturing, and development of process maturity.

In fact, VSIA’s 10th Development Working Group is a quality study group that among other things focuses on how best to implement communications and interfaces, conduct verification, quantify signal integrity, and protect IP developers against unauthorized use of their designs. Consequently, IP providers as well as IP integrators will be able to use common attributes to speedily assess the quality of single IP blocks or entire SoCs.

Key constraints

The shorter a product life cycle, the greater the pressure on the SoC design process to meet time-to-market and time-to-volume goals. Digital IC designs of medium complexity may have found 18-24 months ample for development to market; but now only six months are allowed for multimedia, wireless, and cryptography designs of highly complex SoCs having analog elements.

Consider that a 20-month development phase for a design team of 10 engineers can exceed $225 000 per engineer per year for salaries and overhead alone, translating into development costs of roughly $4.5 million. Clearly, a shorter time to market will cut costs on the front end, as well as generate larger revenues over the longer term. And productivity will be enhanced through improvements to existing EDA tools, new ways of utilizing these tools, and wide deployment of reusable IP into the SoC.

For SoCs of up to medium complexity, computer-aided design tools are widely used to optimize design flow. But it is often difficult, at times impossible, to map complex system requirements comprehensively into a synthesizable high-level architecture. So EDA tools must make doubly sure that the designer’s space, power, and timing constraints can be met prior to fabrication.

Another challenge arises from incorporating analog functions into the digital design flow. Conservative predictions indicate that such SoCs will have grown from below 20 percent of the total SoC count in 1997 to more than 60 percent by the end of this year, surpassing $22 billion in total mixed-signal IC revenue. This is obviously a commercial incentive.