So far, we’ve discussed the design of analog and digital ICs. In this overview, we’ll take a look at the broad strokes of radio frequency (RF) integrated circuit design.

RFIC Design Considerations

Contents

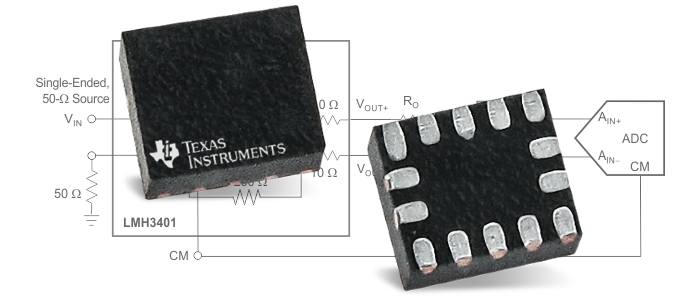

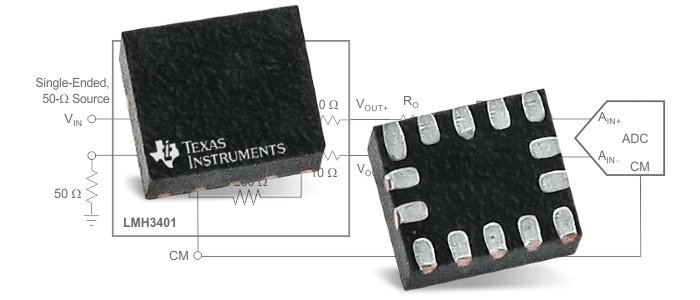

RF IC design, much like niche areas of analog IC design, is often a custom process that is aided by one, or often, many EDA tools. Part of the precise nature of RF IC design is that parasitics and packaging characteristics have first-order impact on the performance of RF circuits. Therefore, RF IC design is often an iterative process that involves the extensive use of EM simulation, parasitic modeling, and package modeling throughout the IC design process.

The LMH3401, a fully differential amplifier optimized for RF applications. Image used courtesy of Texas Instruments

System Budget Parameters

RF IC designs are also given performance requirements and constraints in terms of a “system budget” for key parameters, such as noise figure, power, phase noise, harmonics, linearity, etc. This budgeting is determined by the system-level design team, which passes on budget constraints and performance requirements to the RF designers responsible for each block in the system diagram. These blocks are further broken down into topologies and circuits that undergo an iterative process of design, simulation, and optimization and layout simulation using EM simulation tools that can handle ICs.

IC Design Constraints

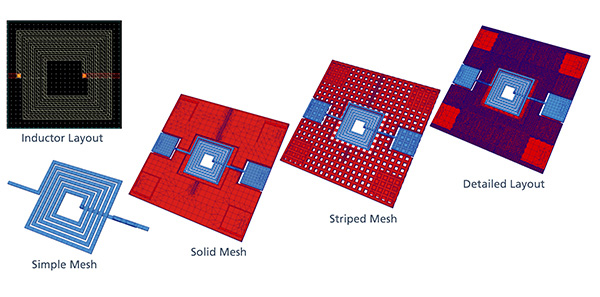

As some on-chip passives such as inductors and capacitors are heavily constrained by the foundry, RF IC designers often have limited control of the sizing and values of these components. This leads to greater uncertainty in design, and possibly the need to design and test new components in a back-and-forth process with the foundry to yield components that best meet the needs of the RF circuits.

In some cases, additional modeling of bond-wires and other packaging dynamics unrelated to the foundry may be needed by RF designers to accurately predict parasitics and final device performance in end-assembly. Many RFICs are delivered as bare die and are wire-bonded directly into an assembly or pallet instead of typical IC packaging and PCB placement.

EM Simulation

Once an RF IC is in the physical layout phase, there will often be several iterations of EM simulation, circuit simulation, and parasitic extraction that involves at least the IC package, but may also take into account the PCB and external circuits of a device. The reason for this is that RF circuits, much like highly sensitive analog circuits, can experience dramatic performance changes due to nearby external circuits, electric/magnetic fields, temperature, electromagnetic signals, and other environmental factors.

Even after tape-out, testing, model enhancement, and additional optimization is often needed before a final design is submitted and RFIC production begins.

Multi-layout conditioning for EM modeling as a function of RF design EDA tools. Image used courtesy of Cadence

RF Abstraction Levels

Below are the general abstraction levels for RF ICs:

- Functional

- Behavioral

- Macro

- Circuit

- Transistor

- Physical layout

RFIC Design Flow

The following describes the workflow that an engineer may follow to design an RF integrated circuit:

- Design specification

- Specifications

- Constraints

- Topologies

- Test bench development

- System design

- High-level system design and budgeting

- Behavioral modeling

- Circuit Synthesis

- HDL Mixed-level SIM

- Mixed-level partitioning

- Circuit Design

- Use of foundry design kit

- Spiral inductor synthesis/modeling

- Detailed circuit design

- Circuit Simulation

- Time domain

- Frequency domain

- Physical Design

- Layout

- Electromagnetic simulation and extraction

- Parasitic extraction

- Extraction of on-chip passives

- Extraction of package parasitics

- Design rules check (DRC)

- Layout versus schematic (LVS)

- Verification in systems test bench

- Sign-off Net extraction/Tape-out

In the final part of this series, we’ll look at mixed-signal IC design.