Synopsys, one of the largest vendors of electronic-design-automation (EDA) software, rolled out a unified suite of simulation software that promises to speed up the design of systems-on-a-chip (SoCs), systems-in-package (SiPs), and memory chips for use in data centers, 5G, automotive, artificial intelligence (AI), and other areas.

Today, the most advanced chips have billions of transistors, but it is impossible for engineers to verify by hand every single facet of the chip before it is manufactured. Failure to accurately test the blueprint of a chip for mistakes can drag out the development process and raise the possibility of a premature failure in the device in the future, which can damage a company’s reputation.

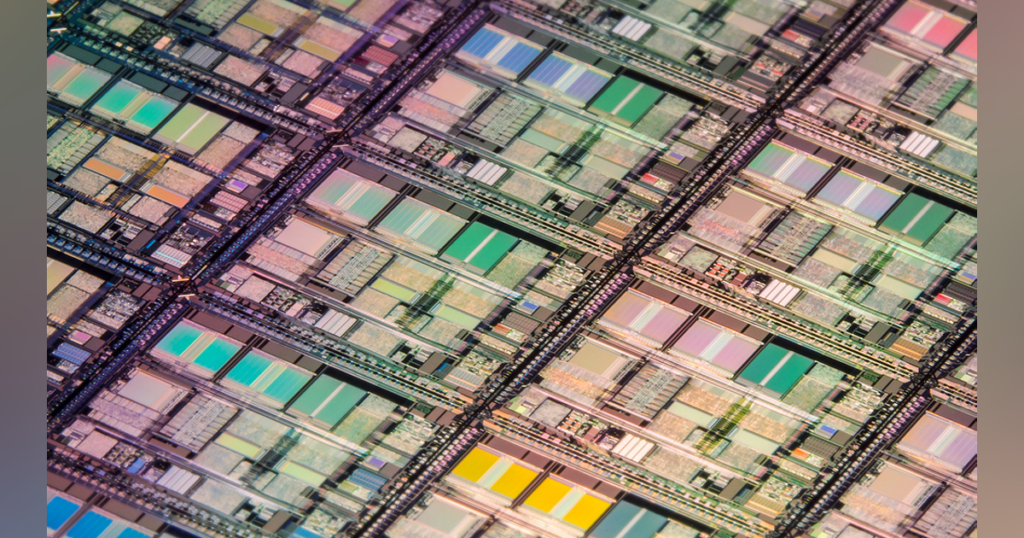

“EDA is the unknown soldier of the semiconductor design process,” said Hany Elhak, who handles product management and marketing for the custom IC and physical verification group at Synopsys. But as chips have become vastly more complicated in recent years, circuit simulation software has become an indispensable part of every engineer’s toolbox (Fig.1).

%{[ data-embed-type=”image” data-embed-id=”607e0705a6ade9d3368b48e2″ data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”Synopsys Spice 1″ data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/04/Synopsys_SPICE_1.607e07043ac08.png?auto=format&fit=max&w=1440″ data-embed-caption=”” data-embed-credit=”Figure 1. (Image courtesy of Synopsys).” ]}%

Synopsys sells software tools based on the industry-standard SPICE simulation technology. SPICE is used to create a computer model of an analog or other electronic circuit and put it through its paces to test whether it works as intended. SPICE can also be used to identify potential areas for improvement and test planned changes to the design without being forced to prototype it.

But when it comes to SoCs or SiPs consisting of memory, analog, radio frequency (RF), digital, and other blocks of intellectual property (IP) on the same silicon die or package, vendors have had to use different design and verification tools for every part of the IC. But according to Synopsys, these disparate tools are not cut out for huge amount of complexity in modern chips.

The electronic design software giant said that it integrated all its simulation software into a single solution, PrimeSim Continuum, aimed at analog, mixed-signal, RF, and custom digital memory designs. The all-in-one system allows its customers to mix and match different simulation engines (Fig. 2) to simulate different parts of the SoC and run them all from the same environment.

%{[ data-embed-type=”image” data-embed-id=”607e0705fdc914194c8b48ad” data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”Synopsys Spice 2″ data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/04/Synopsys_SPICE_2.607e0704491ac.png?auto=format&fit=max&w=1440″ data-embed-caption=”” data-embed-credit=”Figure 2. (Image courtesy of Synopsys).” ]}%

To boost productivity, Synopsys said it enhanced the SPICE and FastSPICE architectures at the heart of the software, giving it the speed and capacity to test semiconductor designs up to 10 times faster than previously without giving up the accuracy of the analysis. Synopsys said PrimeSim Continuum can shorten the time it takes to bring products to market and, in turn, reduce costs.

As the semiconductor industry crams more and more transistors on tiny squares of silicon, Synopsys is trying to keep up with the needs of chip vendors with faster and more accurate simulation software.

Synopsys said more of its customers are bringing power management ICs, radio frequency ICs, and other analog chips previously slapped on the circuit board (PCB) in a smartphone or other device on the same slice of silicon as the CPU, I/O, and memory. These increasingly heterogeneous SoCs are also housing larger slices of embedded memory and faster I/O. (Fig. 3).

%{[ data-embed-type=”image” data-embed-id=”607e07058f14e6da168b45b1″ data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”Synopsys Spice 6″ data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/04/Synopsys_SPICE_6.607e07044c9ce.png?auto=format&fit=max&w=1440″ data-embed-caption=”” data-embed-credit=”Figure 3. (Image courtesy of Synopsys).” ]}%

Another problem on the semiconductor industry’s plate is increased parasitics—or unwanted resistance, inductance, or capacitance in electronic circuits—as these types of chips scale to smaller and smaller nodes. The analog parts of the IC are also more vulnerable to variations that occur as a result of the IC production process. These slight aberrations can cause bugs or a complete failure of the IC in the future, adding to the challenges of verification.

Instead of loading all the different components of a smartphone or other device on a single die, other vendors are rolling out chips based on a system-in-package, or SiP, approach. That opens the door for vendors to create many different chips based on different nodes and then seal them all up together to wring out more performance, reduce power, or add new features.

“It is both scale complexity and system complexity that have been increasing,” Elhak said. “You need to simulate not only the chip itself but at the same time all its interactions with other chips in the package,” he added. The result is more simulations with longer runtimes and higher levels of accuracy to weed out potential weaknesses in the blueprint of the chip.

Synopsys said its latest solution brings together a wide range of different simulation engines in a single environment that is engineered for ease of use and improved productivity (Fig. 4).

%{[ data-embed-type=”image” data-embed-id=”607e07053903c565168b4598″ data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”Synopsys Spice 5″ data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/04/Synopsys_SPICE_5.607e07043bf6e.png?auto=format&fit=max&w=1440″ data-embed-caption=”” data-embed-credit=”Figure 4. (Image courtesy of Synopsys).” ]}%

The all-in-one solution includes its PrimeSim SPICE technology for analog, radio frequency, and digital verification; PrimeSim HSPICE, its gold-standard signoff software for foundation IP as well as signal and power integrity; PrimeSim XA, a FastSPICE tool for mixed-signal SoC and SRAM designs; and PrimeSim Pro, its latest FastSPICE architecture for DRAM and flash-memory chips. Linking them all together is PrimeWave, its new design environment.

“All of these engines are combined in a single, unified solution,” Elhak said. “We allow you to use the right engine for any of the technologies you’re verifying.” Synopsys said PrimeSim is one of the cornerstones of its custom design platform, and it is also integrated with its suite of verification software so that customers can resolve problems that turn up in PrimeSim.

Synopsys said the tools are currently being used by Samsung Electronics, NVIDIA, and other early-access customers. The company’s major rivals are EDA heavyweights Cadence Design Systems and Siemens EDA.

%{[ data-embed-type=”image” data-embed-id=”607e0705a6ade973668b4783″ data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”Synopsys Spice 3″ data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/04/Synopsys_SPICE_3.607e07044e582.png?auto=format&fit=max&w=1440″ data-embed-caption=”” data-embed-credit=”Figure 5. (Image courtesy of Synopsys).” ]}%

EDA software uses huge amounts of computational horsepower, and semiconductor giants maintain colossal data centers or rent out computing power over the cloud to run them. But creating computer models of electronic circuits with millions to billions of elements and then testing them all out can still take a day or more. “SPICE is the bottleneck for signing off any large chip design,” Elhak warned.

Today, semiconductor firms run thousands of simulations on the most intricately designed chips before sending the final blueprint to a foundry to be manufactured. That further drags out the chip design process.

Synopsys is trying to solve the speed bottleneck with its state-of-the-art SPICE architecture. The company said that it delivers up to three times faster performance for analog, memory, RF, and other IC designs by scaling across CPU cores. Synopsys said it can wring out up to 10 times more performance by taking advantage of accelerated computing on NVIDIA GPUs, without giving up accuracy (Fig. 5).

%{[ data-embed-type=”image” data-embed-id=”607e0705a6ade97d668b476b” data-embed-element=”span” data-embed-size=”640w” data-embed-alt=”Synopsys Spice 4″ data-embed-src=”https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2021/04/Synopsys_SPICE_4.607e070441218.png?auto=format&fit=max&w=1440″ data-embed-caption=”” data-embed-credit=”Figure 6. (Image courtesy of Synopsys).” ]}%

“As modern compute workloads evolve, the scale and complexity of analog IC designs have moved beyond the capacity of traditional circuit simulators,” said Edward Lee, vice president of mixed-signal design at NVIDIA, in a statement. He said that the improvements in PrimeSim SPICE shorten the time it takes to carry out verification on analog ICs from days to hours.

Synopsys said it upgraded its underlying FastSPICE architecture to model more advanced 3D DRAM—including high-bandwidth memory (HBM) used in data centers—and flash-memory chip designs. The PrimeSim Pro tool uses advanced partitioning and modeling technologies to split simulations into more manageable parts, promising two to five times the speed of other solutions on the market (Fig. 6).

“Relentless technology scaling and innovations around DRAM architecture have resulted in larger and more complex memory designs requiring higher simulation performance and capacity,” said Jung Yun Choi, corporate vice president of memory design technology at Samsung. He added that PrimeSim Pro could “keep pace with the capacity needs of our advanced memory designs and allow us to meet our aggressive time-to-results targets.”

Synopsys said PrimeSim XA, PrimeSim HSPICE, PrimeSim SPICE, and PrimeSim Pro are all supported by leading foundries, including TSMC and Samsung, on advanced process nodes.