Microsemi, a wholly-owned subsidiary of Microchip Technology, produces a portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. In addition to high-performance and radiation-hardened analog/mixed-signal integrated circuits, FPGAs, SoCs and ASICs, they also design power management products, timing and synchronization devices, voice processing devices, radio frequency (RF) solutions, enterprise storage and communication solutions, security technologies, scalable anti-tamper products, and Ethernet solutions. Designing such a broad range of products intended for multiple specialized industries and applications requires Microsemi designers to work in both mature and leading-edge technology nodes.

The complexity of design rule checking (DRC) closure for advanced technology nodes (20nm and below) is commonly recognized and actively attended to by both the design and electronic design automation (EDA) communities. What is less frequently acknowledged, however, is the time it still takes to close DRC for mature node designs. Despite their maturity, these nodes face many of the same DRC pressures as leading-edge nodes in terms of rule and check growth and complexity.

The most profitable use of any custom layout designer’s time is in optimizing a design to meet the desired power, performance, and area (PPA) metrics. Every minute spent finding and fixing DRC errors takes valuable time away from design optimization activities. Even if designers run DRC on small cells, blocks, or partial windows of large cells, the overhead involved in writing out the GDSII file and launching a batch DRC run (including the wait time for a machine to be available in the compute farm) ends up taking minutes instead of seconds. While that doesn’t seem like much for one DRC run, over a course of a design tapeout cycle, these little time extensions can easily add up to weeks of your total cycle time—time that could be more profitably spent optimizing designs for a better bottom line.

Microsemi’s in-design DRC flow

Microsemi uses a robust batch Calibre nmDRC flow that is optimized for their signoff DRC runs. However, they were looking for ways to further accelerate their DRC productivity, such as enabling in-design signoff-quality DRC during earlier stages of the design flow. The goal was to give their designers the opportunity to quickly perform a what-if analysis of possible edits to fix DRC errors during design, enabling them to implement an optimum fix at a point when changes were relatively easier to implement. By checking their designs and fixes against a signoff rule deck, designers could also be confident that the changes they implemented would be DRC-clean at tapeout.

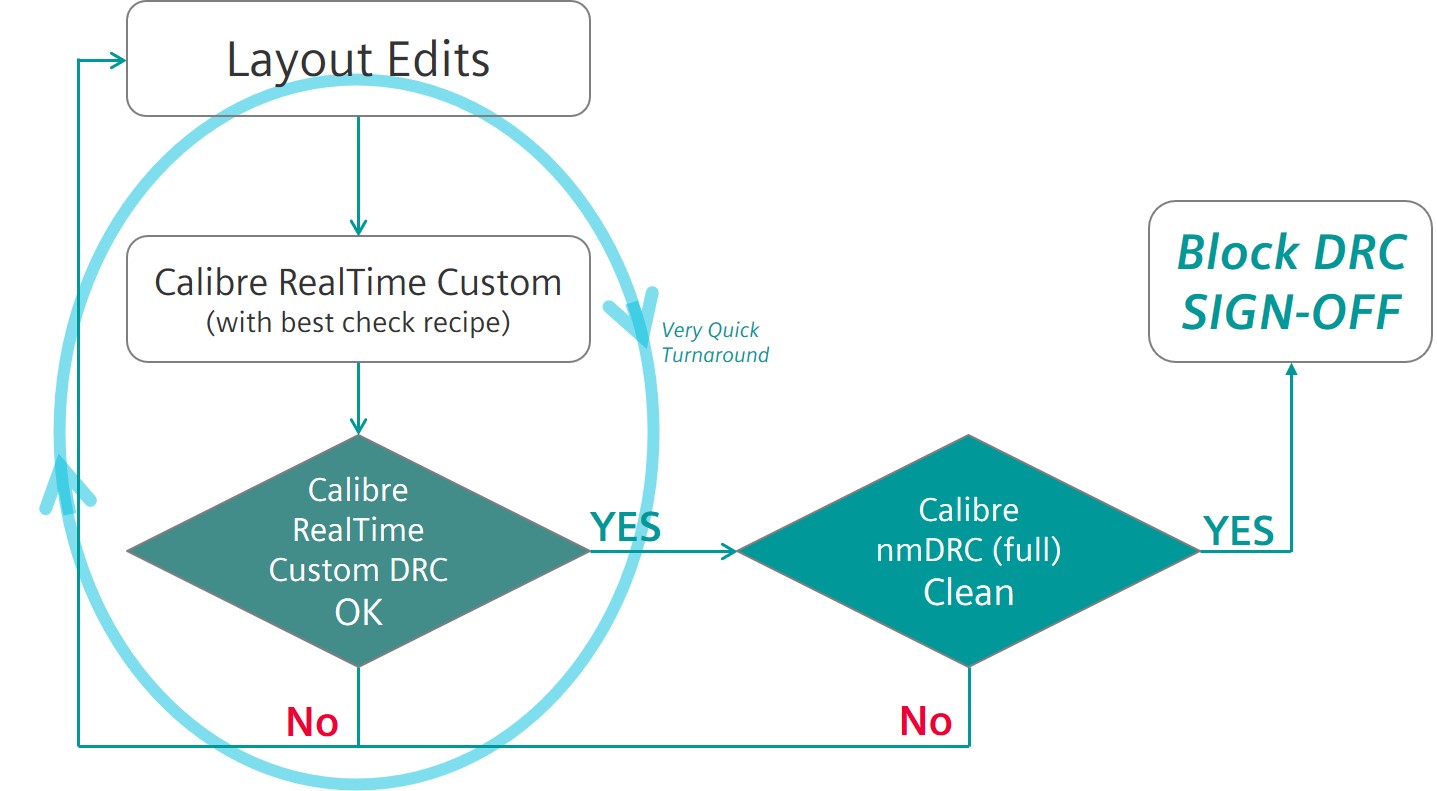

The Calibre RealTime Custom interface enables in-design signoff-quality Calibre DRC during custom and analog/mixed-signal (AMS) design flows, improving both design speed and the quality of results by providing immediate signoff-quality feedback on design rule violations. Integrated within custom design tools, the Calibre RealTime Custom interface provides direct calls to Calibre analysis engines running foundry-qualified Calibre rule decks. These Calibre engines perform fast, incremental checking in the design window, providing immediate feedback on design rule violations. The intelligent guidance provided in this feedback enables designers to quickly optimize designs for PPA without requiring numerous time-consuming design-verification iterations, and with the confidence that the fix is DRC-clean (figure 1).

Fig. 1: The platform changes the traditional layout-verification simulation loop by bringing sign-off quality DRC into the custom/AMS design creation process.

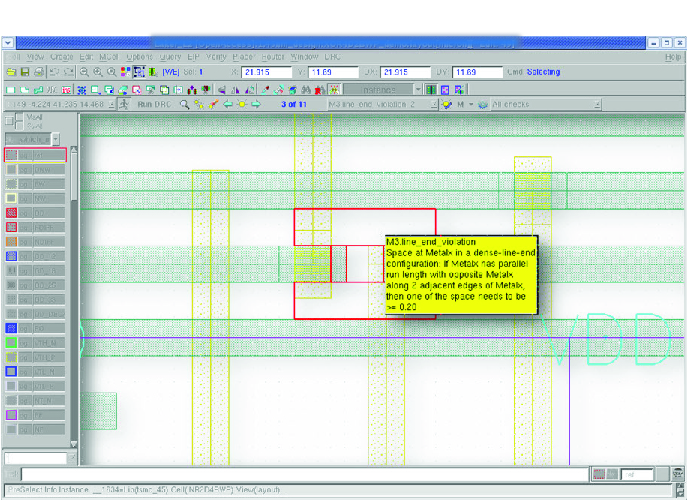

In addition to standard DRC, designers also have the option to select a custom set of checks (check recipes) that are applicable to the current design window and stage (figure 2). Check recipes enable designers to perform DRC debug in a systematic and prioritized manner based on the design and company requirements, further accelerating the DRC closure time.

Fig. 2: Calibre RealTime Custom in-design DRC flow at Microsemi.

Results

Local edits on Metal and VIA layers

During their custom design flow, Microsemi designers made an engineering change order (ECO) edit on the Metal1, VIA1, and Metal2 layers in a 28nm design. The design GDSII database was 0.5GB in size, containing millions of geometries. Streaming out the entire GDSII file and running batch DRC for an ECO change on Metal 1, VIA1 and Metal 2 layers would have been time-consuming and tedious. Instead, Microsemi designers used the Calibre RealTime Custom interface to perform immediate signoff DRC checking in the local design windows in which the ECO changes were made. Not only were they able to get quick confirmation that the changes were DRC-clean, but using in-design DRC also eliminated the need for intermediate batch DRC runs.

Check recipes

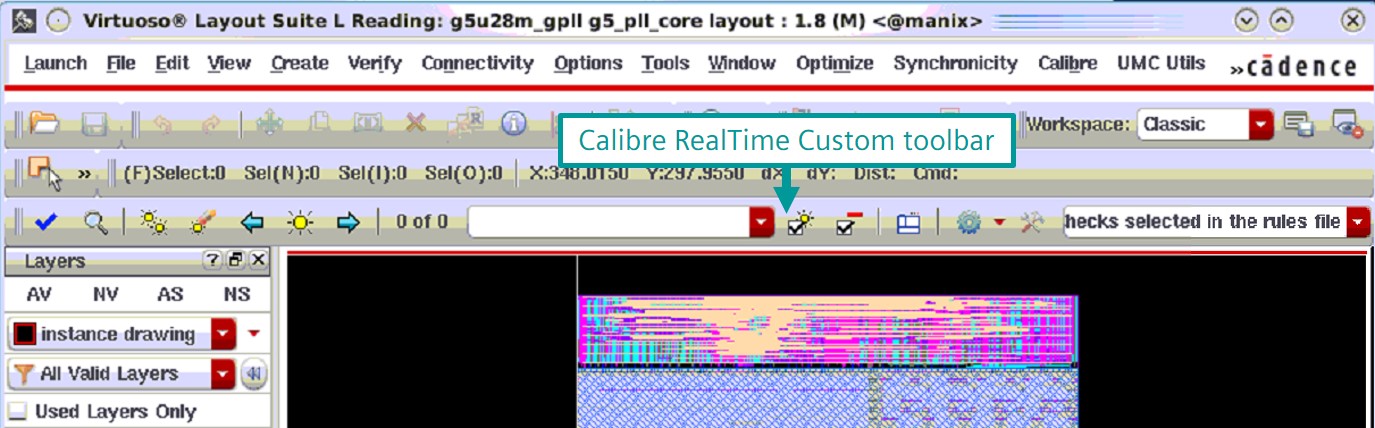

Microsemi designers also harnessed the power of the built-in check recipes in the Calibre RealTime Custom tool to significantly reduce the number of DRC checks executed, which not only accelerated the DRC run, but also resulted in fewer (but more relevant) DRC results, making DRC debug easier and faster as well. The designers used the integrated toolbar in their design environment (figure 3) to select the built-in visible layers check recipe, turn on the visibility of the Metal1, Via1 and Metal 2 layers, and turn off all other layers. Using the visible layers check recipe resulted in an immediate reduction from over 5.5K checks to only 250, with no special setup required.

Fig. 3: An integrated Calibre RealTime custom toolbar simplifies invocation and option selection.

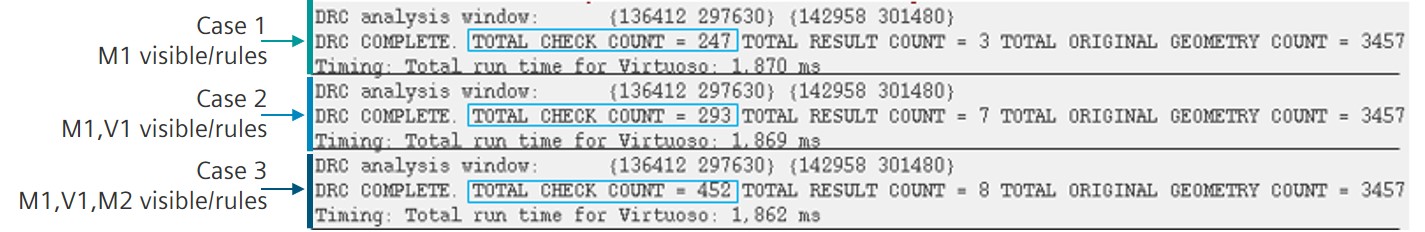

Reviewing the results of the three-layer combinations reveals the DRC run took fewer than 2 seconds for each case (figure 4).

Fig. 4: Calibre RealTime Custom check recipe runtimes and results for selected layer combinations.

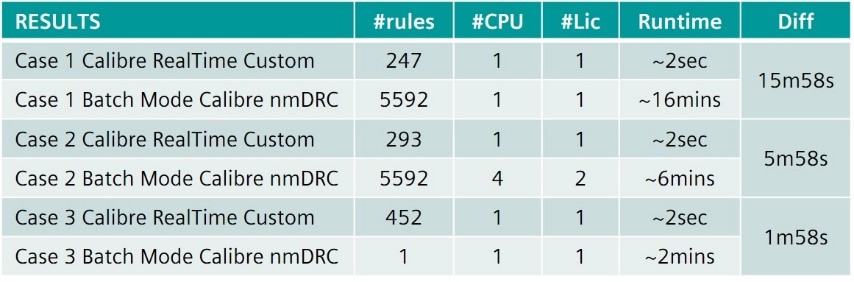

For comparison, running batch DRC jobs on the same design area would result in runtimes ranging from 2 minutes (a single check) to 16 minutes. Figure 5 shows a comparison of Calibre RealTime Custom and batch DRC runs for a single iteration on the three cases from figure 4. Over the course of a design cycle, designers would typically need to run multiple batch DRC iterations. By using in-design DRC and eliminating the need for most intermediate batch DRC runs, Microsemi achieved a productivity improvement of 2-4X, shaving weeks off the tapeout schedule for their mature node designs.

Fig. 5: Comparison of Calibre RealTime Custom check recipe and batch DRC runtimes for a 28nm design.

Tapeout edits

During the tapeout stage, Microsemi designers almost always end up performing critical physical verification and debug on a particular region or on a specific block. For example, they may need to quickly fix last-minute DRC errors, review the count and accuracy of DRC/DFM results, or compare the different values specified by a particular check to determine the best way to fix a DRC error.

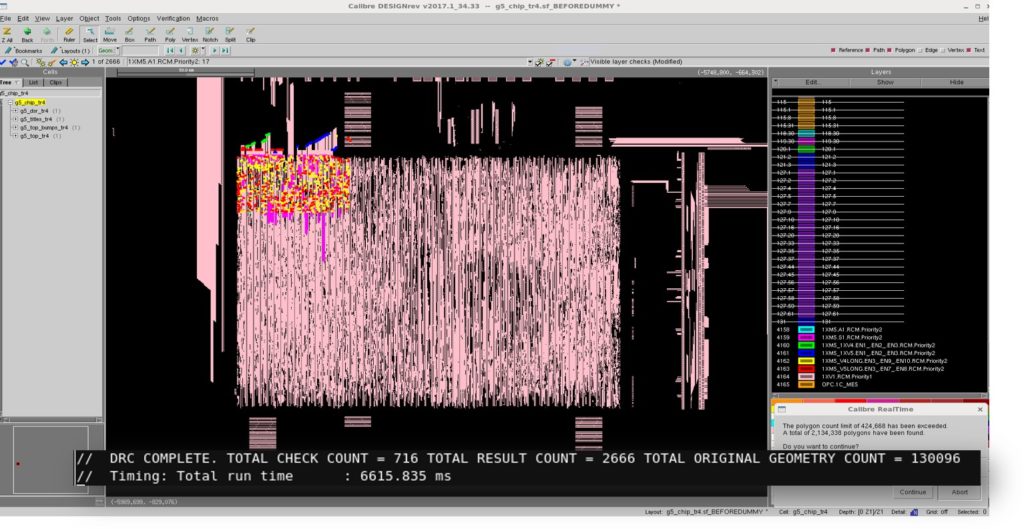

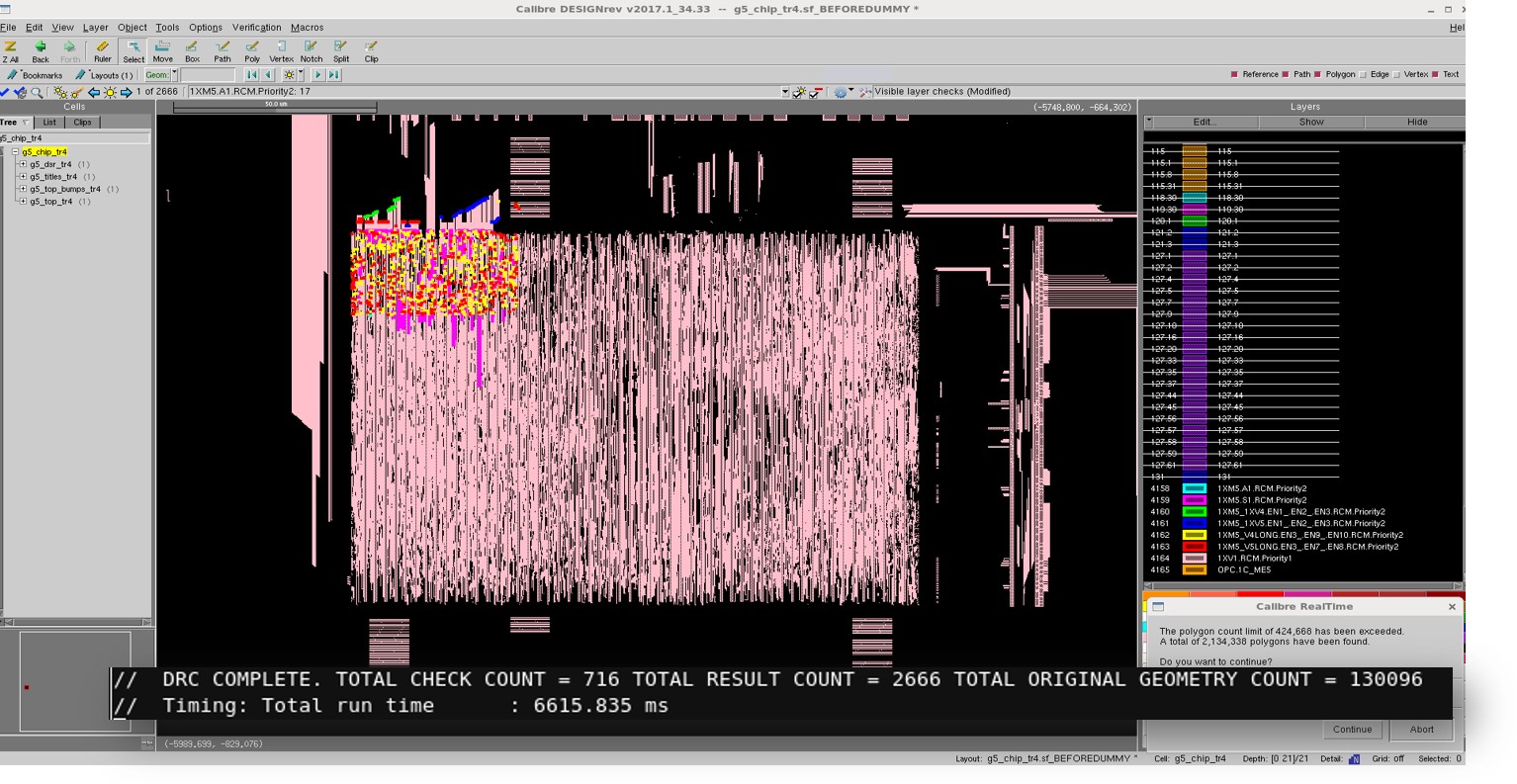

Microsemi designers used the fast-loading capabilities of the Calibre DESIGNrev layout viewer to load the entire design, then employed its editing capabilities to apply fixes for DRC errors. For every fix, they used the Calibre RealTime Custom interface to get immediate DRC feedback. This instant feedback not only confirmed the fixes were DRC-clean, but it also provided designers time to implement multiple fixes, if needed, to iterate towards an optimal solution.

Fig. 6: Using Calibre RealTime Custom in-design DRC in the Calibre DESIGNrev viewer for physical verification review at tapeout.

Conclusion

Microsemi produces a wide range of specialized chips that are used for multiple purposes across a variety of industries, using both mature and advanced process nodes. While advanced nodes were expected to be more complex, they found that even in mature node design implementation, layout designers were spending a significant amount of their valuable time fixing DRC errors—time that could be more beneficially spent ensuring their designs meet their PPA goals. By replacing their intermediate batch DRC runs with the immediate signoff-quality DRC feedback provided by the Calibre RealTime Custom interface, Microsemi designers were able to not only improve overall DRC productivity by 2-4X, but also implement DRC fixes that optimized their design PPA. Accelerating DRC closure for their designs and reducing tapeout time by weeks allowed Microsemi to reap the benefits of achieving first-to-market success, while enhancing their ability to deliver designs optimized for PPA helped ensure their products met or exceeded market expectations.